# AN INTERCONNECT-DRIVEN SYSTEM-ON-CHIP FLOORPLANNING FRAMEWORK

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Patrick Siu-ying Hung August 2002

$\odot$  Copyright 2002 by Patrick Siu-ying Hung All Rights Reserved

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Michael J. Flynn (Principal Adviser)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Giovanni De Micheli

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

John T. Gill III

Approved for the University Committee on Graduate Studies:

### **Preface**

As VLSI technology reaches deep submicron era, interconnect properties instead of gate properties plays a dominant role in determining processor performance and power consumption. While this relationship has been known for a number of years, most System-On-Chip (SOC) vendors today still follow the traditional design flow, separating architectural design, logic design and physical design into three distinct stages. Chip floorplanning, which affects architectural and logic design and determines the overall system performance, is often performed only in the physical layout stage. This is one of the main reasons why many SOC's have problems surpassing 400MHz, while custom-made, high-end processors have already exceeded 2.5GHz.

The focus of our research is to develop an interconnect-driven floorplanning framework, supporting effective chip floorplanning in the architectural design stage. In order to estimate the effects of interconnect in the early design stages, we examine interconnect models on three different levels. First, we developed a wirelength distribution model within a functional block. Our proposed wirelength distribution model is more flexible and accurate than the previous models. It can be used to estimate wire load, wire delay and interconnect power consumption within a synthesized functional block. Second, we developed a wire congestion model, identifying congestion hotspots among multiple blocks in a floorplan. The model can be used to model the effects of interconnect coupling in a floorplan. Third, we developed an interconnect-driven processor performance model, which generalizes the relationship between processor performance and interconnect overhead.

The three interconnect models, constituting the basis of our research, were integrated with other design tools previously developed in our research group to form a unified floor-planning framework. Our research shows that system-level floorplanning in the architectural design stage is necessary in the deep-submicron era.

# Acknowledgments

First, and foremost, I would like to thank my advisor, Professor Michael J. Flynn, for his superb technical guidance and generous financial support in the past few years. Most importantly, he taught me how to conduct independent research, which will continue to be an invaluable asset for me for the rest of my life. I would also like to express my gratitude to Professor De Micheli and Professor John Gill, who carefully read through this dissertation and provided many constructive comments.

There are many other people to whom I owe a debt of appreciation for their assistance and support to the preparation and completion of this work. I would like to thank Susan Gere, who helped maintain a friendly and stable research environment for all graduate students. I would like to thank the current and previous members of my research group, especially Professor Martin Morf, Professor Sang Bang Choi, Professor Neville Harris, James Bennett, Takahiro Nishiyama, Kevin Rudd, Steve Fu, Grant McFarland, Albert Liddicoat, Hossam Fahmy and Andrew Zimmerman. They have spent countless hours with me discussing on my research, and have proved to be my best sounding board. I would like to thank Luc Séméria, who worked with me on the statistical wirelength distribution model.

Last, but definitely not least, I would like to thank my wife for her unfailing moral support during my years at Stanford. Without whom none of this work would have been possible.

# Contents

| P            | refac | e                  |                                                | iv |

|--------------|-------|--------------------|------------------------------------------------|----|

| $\mathbf{A}$ | ckno  | wledgm             | ${f ents}$                                     | v  |

| 1            | Intr  | oductio            | on                                             | 1  |

|              | 1.1   | On-Chi             | ip Interconnect System                         | 1  |

|              | 1.2   | Deep S             | Submicron Interconnect Issues                  | 3  |

|              |       | 1.2.1              | System Performance                             | 5  |

|              |       | 1.2.2              | Power Dissipation                              | 6  |

|              |       | 1.2.3              | Reliability and Manufacturing Yield            | 7  |

|              |       | 1.2.4              | Signal Integrity                               | 8  |

|              | 1.3   | Our W              | ork                                            | 8  |

|              |       | 1.3.1              | Motivation                                     | 8  |

|              |       | 1.3.2              | A Priori Interconnect Models                   | 11 |

|              | 1.4   | Organi             | zation of this Dissertation                    | 11 |

| 2            | Wir   | $\mathbf{elength}$ | n Distribution Model                           | 13 |

|              | 2.1   | Introdu            | action                                         | 13 |

|              | 2.2   | Wirelei            | ngth Distribution Model for Rectilinear Blocks | 15 |

|              |       | 2.2.1              | Effects of Block Aspect Ratio                  | 15 |

|              |       | 2.2.2              | Effects of Routing Obstacles                   | 19 |

|              | 2.3   | Experi             | mental Results                                 | 21 |

|              |       | 2.3.1              | Average Wirelength Model                       | 22 |

|              |       | 2.3.2              | Wirelength Distribution Model                  | 25 |

|              | 2.4   |                    | ary                                            | 28 |

| 3 | Wir        | e Cong | gestion Model                                  | 29 |

|---|------------|--------|------------------------------------------------|----|

|   | 3.1        | Introd | uction                                         | 29 |

|   | 3.2        | Wire ( | Congestion Model                               | 30 |

|   |            | 3.2.1  | Problem Formulation                            | 30 |

|   |            | 3.2.2  | Algorithm                                      | 36 |

|   |            | 3.2.3  | Experimental Results                           | 40 |

|   | 3.3        | Floorp | olan Optimizer                                 | 44 |

|   |            | 3.3.1  | Problem Formulation                            | 44 |

|   |            | 3.3.2  | Algorithm                                      | 49 |

|   |            | 3.3.3  | Experimental Results                           | 52 |

|   | 3.4        | Summ   | ary                                            | 54 |

| 4 | Pro        | cessor | Performance Model                              | 55 |

|   | 4.1        | Introd | $\operatorname{uction}$                        | 55 |

|   | 4.2        | Proble | m Formulation                                  | 57 |

|   |            | 4.2.1  | IPC Model                                      | 57 |

|   |            | 4.2.2  | Interconnect/Complexity Overhead Models        | 62 |

|   |            | 4.2.3  | Overhead Examples                              | 63 |

|   |            | 4.2.4  | Upper Bound on Optimum Instruction Issue Width | 65 |

|   | 4.3        | Experi | imental Results                                | 67 |

|   | 4.4        | Discus | sion                                           | 74 |

|   |            | 4.4.1  | Approximation of $N_{opt}$                     | 74 |

|   |            | 4.4.2  | Effects of the Processor Organization          | 74 |

|   |            | 4.4.3  | Technology Trends                              | 75 |

|   | 4.5        | Summ   | ary                                            | 76 |

| 5 | IPL        | AN Fl  | oorplanning Framework                          | 79 |

|   | 5.1        | Introd | $\operatorname{uction}$                        | 79 |

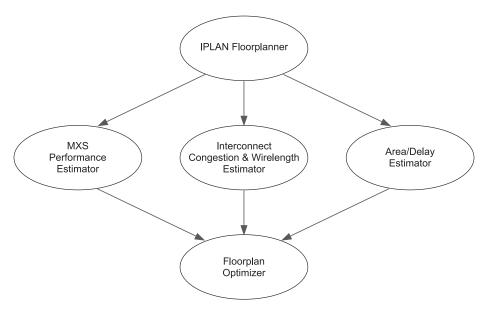

|   | 5.2        | Compo  | onents in IPLAN Framework                      | 81 |

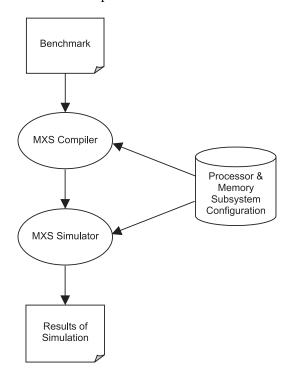

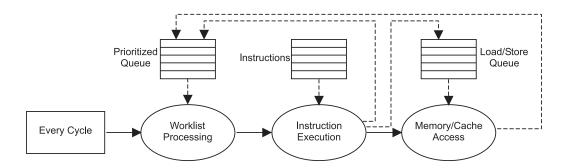

|   |            | 5.2.1  | MXS Performance Simulator                      | 81 |

|   |            | 5.2.2  | Area/Delay Estimator                           | 84 |

|   |            | 5.2.3  | Interconnect Estimator and Floorplan Optimizer | 85 |

|   | 5.3        | Case S | Study                                          | 90 |

|   | 5 <i>1</i> | Cumm   | OPV                                            | 06 |

| 6            | Con   | clusio                  | ns and Future Work                                              | 98    |

|--------------|-------|-------------------------|-----------------------------------------------------------------|-------|

|              | 6.1   | Conclu                  | sions                                                           | 98    |

|              | 6.2   | Contri                  | butions of this Dissertation                                    | 99    |

|              | 6.3   | Future                  | Work                                                            | 100   |

| $\mathbf{A}$ | Stru  | ıctural                 | Wirelength Distribution Function                                | 102   |

|              | A.1   | $\operatorname{Introd}$ | uction                                                          | 102   |

|              | A.2   | Buildi                  | ng Generating Polynomials of One-Dimensional Structures         | 103   |

|              | A.3   | Genera                  | ating Polynomials for More Complicated Architectures            | 104   |

|              |       | A.3.1                   | Rectangular Block                                               | 104   |

|              |       | A.3.2                   | L-Shaped Block                                                  | 106   |

|              |       | A.3.3                   | O-Shaped and C-Shaped Blocks                                    | 108   |

|              |       | A.3.4                   | Comparison of L-Shaped Block, C-Shaped Block and O-Shaped Block | : 110 |

| Bi           | bliog | graphy                  |                                                                 | 111   |

# List of Tables

| 2.1 | Structural Length Distribution Function for the L-shaped Block <sup>1</sup>   | 20  |

|-----|-------------------------------------------------------------------------------|-----|

| 2.2 | Experimental Results on Average Wirelength Estimation                         | 22  |

| 2.3 | Experimental Results on Average Wirelength Estimation                         | 23  |

| 4.1 | Various Interconnect and Complexity Overhead $Models^1$                       | 62  |

| 4.2 | Upper Bounds on $N_{opt}$ for Various Interconnect/Complexity Overhead Models | 67  |

| 4.3 | Functional Unit Latencies                                                     | 68  |

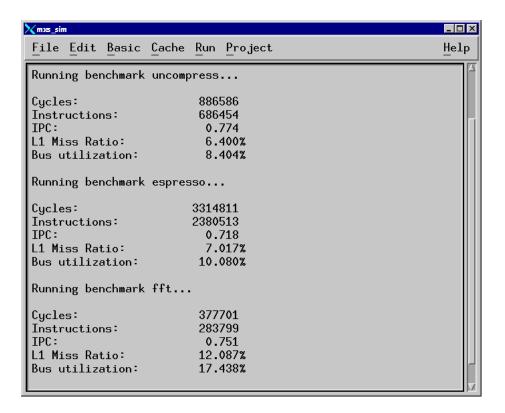

| 4.4 | Benchmarks Simulated Using the MXS Simulation                                 | 68  |

| 5.1 | Lexra's LX4380 Processor Core Baseline Parameters                             | 90  |

| 5.2 | MXS Simulation Results for the Compress Benchmark                             | 91  |

| 5.3 | Comparison between the Original Architecture and the Modified Architecture    |     |

|     | with a Non-pipelined 64KB Data Cache                                          | 93  |

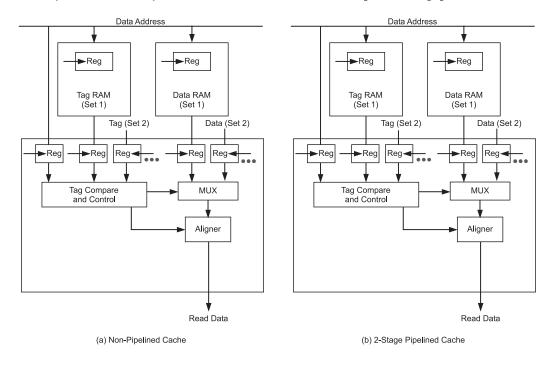

| 5.4 | Comparison between the Original Architecture and the Modified Architecture    |     |

|     | with a 64KB 2-Stage Pipelined Data Cache                                      | 95  |

| 5.5 | Comparison between a 32KB non-pipelined data cache and a 64KB 2-stage         |     |

|     | pipelined data cache in a 2-way superscalar processor                         | 95  |

| 5.6 | Summary of Different Design Alternatives                                      | 96  |

| A.1 | Structural Length Distribution Function for Rectangular Block                 | 106 |

| A.2 | Structural Length Distribution Function for L-Shaped Block                    | 107 |

# List of Figures

| 1.1  | Metal interconnect structure of a chip after etching of dielectric layers [ES00] 1 |

|------|------------------------------------------------------------------------------------|

| 1.2  | Topview of a CMOS Inverter Layout                                                  |

| 1.3  | 3-D View of the Interconnections in a CMOS Inverter                                |

| 1.4  | Cross-sectional View of the Interconnections in an IC                              |

| 1.5  | Total Transistors per Chip from 2001 to 2016                                       |

| 1.6  | On-Chip Clock from 2001 to 2016                                                    |

| 1.7  | Interconnect Delay                                                                 |

| 1.8  | Traditional Design Flow                                                            |

| 1.9  | Lost Revenue                                                                       |

| 2.1  | Rectangular array of $m \times n$ gates                                            |

| 2.2  | Definitions of Blocks A, B, and C                                                  |

| 2.3  | Average Wirelength Estimations vs Aspect Ratio                                     |

| 2.4  | Wire Density Function $i(l)$ for Various Aspect Ratios                             |

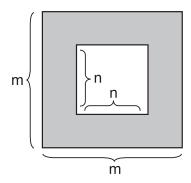

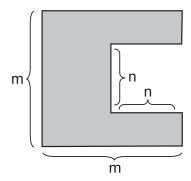

| 2.5  | Routing Obstacle Examples                                                          |

| 2.6  | Wirelength Distributions of L-shaped and Rectangular Blocks                        |

| 2.7  | Average Wirelength vs Aspect Ratio (Cordic)                                        |

| 2.8  | Average Wirelength vs Aspect Ratio (Multiplier)                                    |

| 2.9  | Area vs Aspect Ratio (Multiplier)                                                  |

| 2.10 | Wirelength Distribution with Unity Aspect Ratio (IDCT)                             |

| 2.11 | Wirelength Distribution with Aspect Ratio = 6.0 (IDCT)                             |

| 2.12 | Wirelength Distribution with Routing Obstacles (IDCT)                              |

| 3.1  | Routing between $A(0,0)$ and $B(3, 2)$                                             |

| 3.2  | Routing Probability through a Point                                                |

| 3.3  | Simplified Congestion Model Example                                                |

| 3.4    | Via Minimization Example                                                          | 34  |

|--------|-----------------------------------------------------------------------------------|-----|

| 3.5    | Wire Congestion Routing between Blocks Example                                    | 35  |

| 3.6    | Illustration of Wire Congestion Algorithm                                         | 38  |

| 3.7    | Illustration of Wire Congestion Routing Obstacle Algorithm ( $\alpha=1.0$ )       | 39  |

| 3.8    | Wire Congestion Example: Chip A (Adaptive FIR Filter)                             | 42  |

| 3.9    | Wire Congestion Example: Chip B (16-bit Microprocessor)                           | 43  |

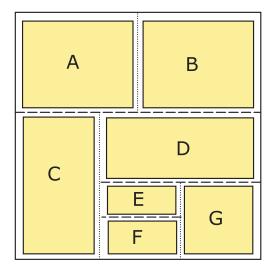

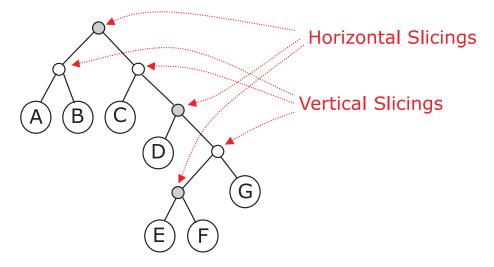

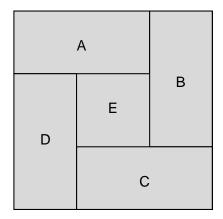

| 3.10   | A Slicing Floorplan Example                                                       | 44  |

| 3.11   | Binary Tree Representation of the Slicing Floorplan                               | 45  |

| 3.12   | A Non-Slicing Floorplan Example                                                   | 46  |

| 3.13   | Sequence Pair Example                                                             | 47  |

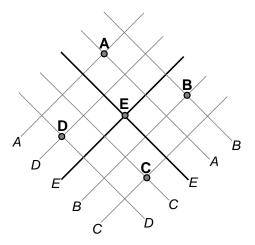

| 3.14   | Sakurai Wire Capacitance Model                                                    | 48  |

| 3.15   | MCNC Benchmark Statistics                                                         | 52  |

| 3.16   | MCNC Benchmark Result                                                             | 53  |

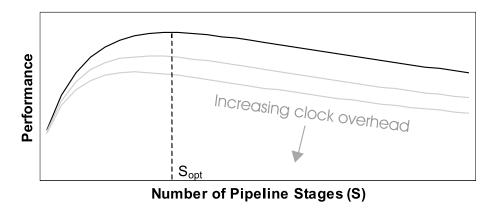

| 4.1    | Processor Performance vs Number of Pipeline Stages                                | 56  |

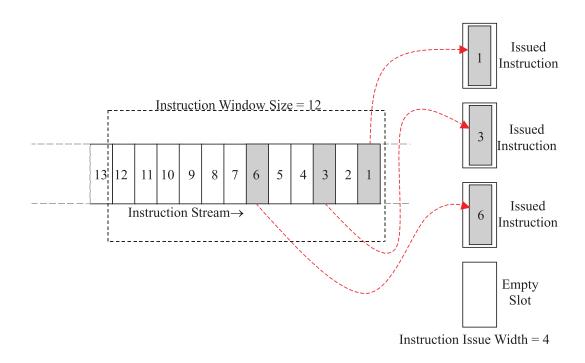

| 4.2    | Instruction Issue in a 4-Way Superscalar Processor                                | 58  |

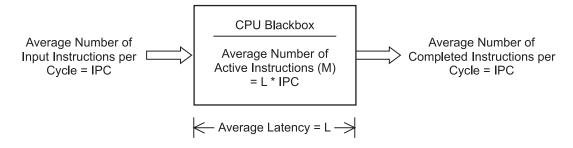

| 4.3    | Number of Active Instructions in a Processor                                      | 59  |

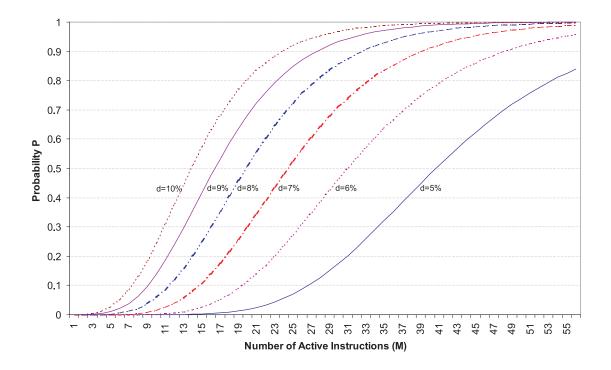

| 4.4    | Relationship between issue slot idle probability $(P)$ and the number of active   | 00  |

| 7.7    | instructions $(M)$ for different instruction dependency probabilities $(d = 5\%,$ |     |

|        | 6%, $7%$ , $8%$ , $9%$ , $10%$ )                                                  | 60  |

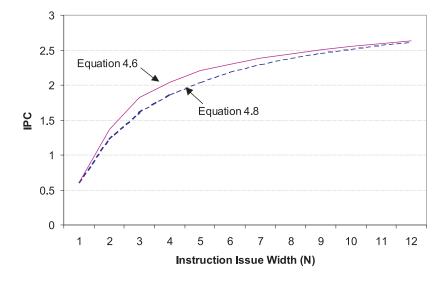

| 4.5    | IPC vs Instruction Issue Width $(N)$ based on Equations 4.6 and 4.8               | 61  |

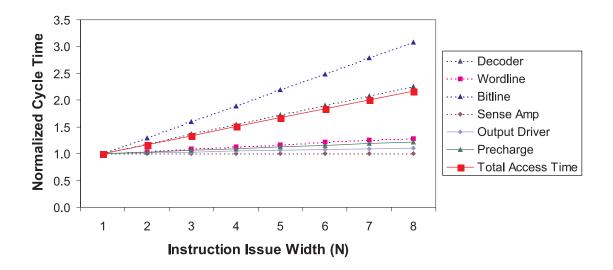

| 4.6    | Register File Access Time vs Instruction Issue Width $(N)$                        | 64  |

| 4.7    | Wakeup Logic Delay vs Instruction Issue Width $(N)$                               | 65  |

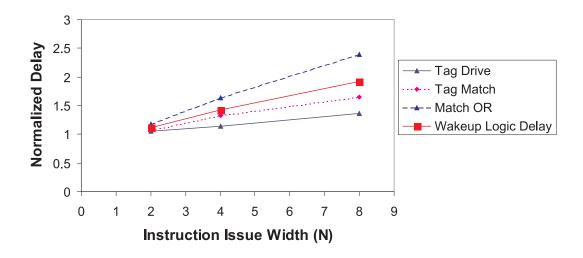

| 4.8    | Relative Performance vs Instruction Issue Width $N$                               | 66  |

| 4.9    | Comparison of the modeled and simulated instructions per cycle (IPC) vs           | 00  |

| 1.0    | instruction issue width (039.wave5)                                               | 69  |

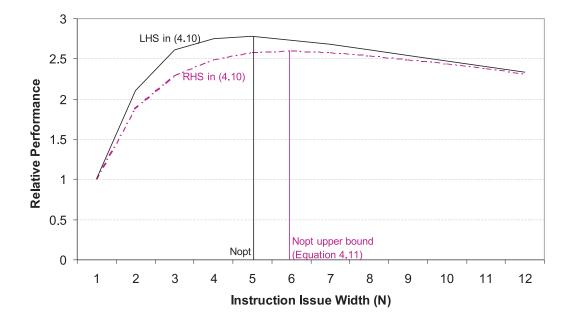

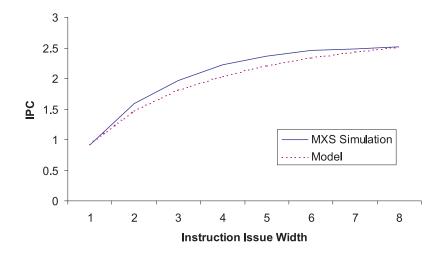

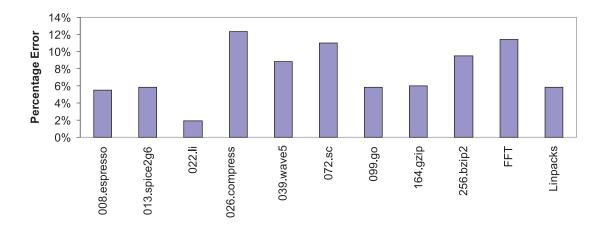

| 4 10   | IPC percentage errors between the model and the MXS simulation                    | 70  |

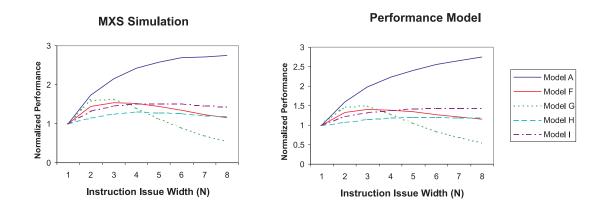

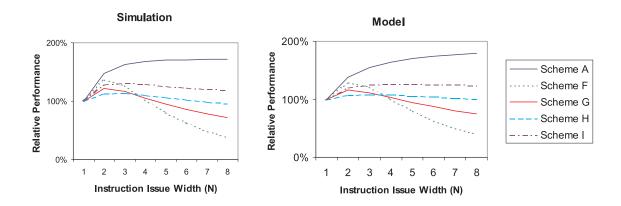

|        | Comparison of the relative performance computed using various overhead            | •0  |

| *• # # | models for the simulated IPC and modeled IPC using the 039.wave5 benchmark.       | 71  |

| 4 19   | Comparison of the relative performance computed using various overhead            | . 1 |

| 1.14   | models for the simulated IPC and modeled IPC based on 008.espresso bench-         |     |

|        | mark                                                                              | 71  |

|        |                                                                                   |     |

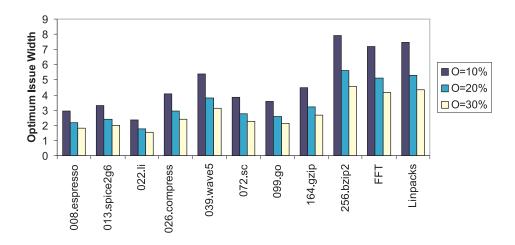

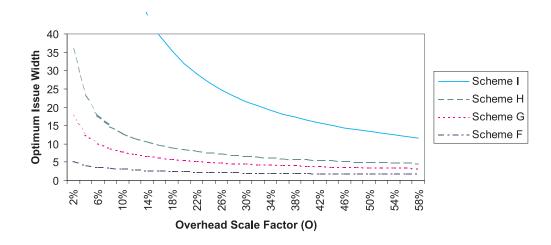

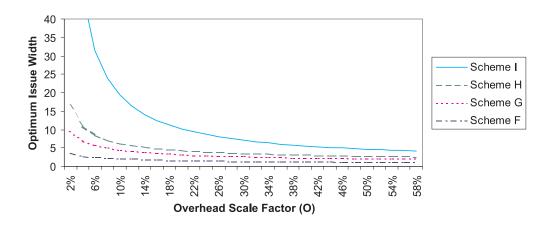

| 4.13 | Optimum instruction issue width for overhead scale factor $\mathcal{O} = 10\%$ , 20%, 30% | 72  |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.14 | Optimum instruction issue width $N_{opt}$ vs overhead scale factor $\mathcal O$ based on  |     |

|      | 256.bzip2 benchmark                                                                       | 73  |

| 4.15 | Optimum instruction issue width $N_{opt}$ vs overhead scale factor $\mathcal O$ based on  |     |

|      | 013.spice2g6 benchmark                                                                    | 73  |

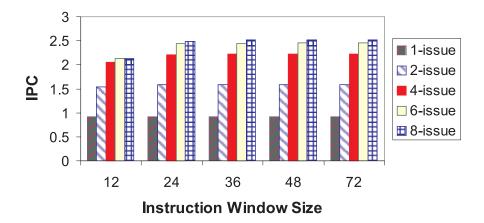

| 4.16 | The instructions per cycle (IPC) as a function of window size and instruction             |     |

|      | issue width                                                                               | 75  |

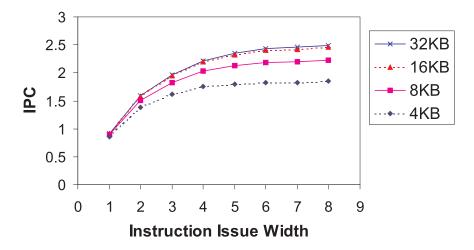

| 4.17 | The instructions per cycle (IPC) as a function of cache size and instruction              |     |

|      | issue width                                                                               | 76  |

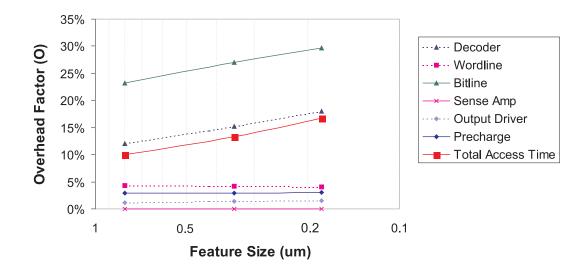

| 4.18 | Overhead scale factor $\mathcal{O}$ vs feature size                                       | 77  |

| 5.1  | Simplified Block Diagram of IPLAN Floorplanning Framework                                 | 80  |

| 5.2  | Simplified MXS Simulator Block Diagram                                                    | 82  |

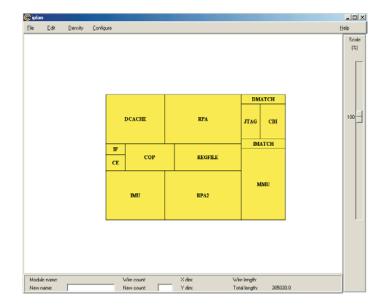

| 5.3  | Simplified MXS Simulation Architecture                                                    | 83  |

| 5.4  | MXS Performance Simulator Graphical User Interface                                        | 84  |

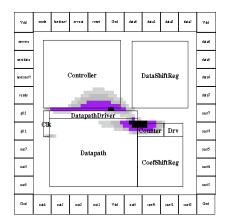

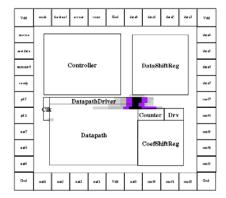

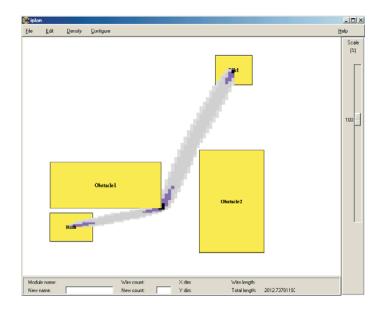

| 5.5  | IPLAN Routing Obstacle Example                                                            | 86  |

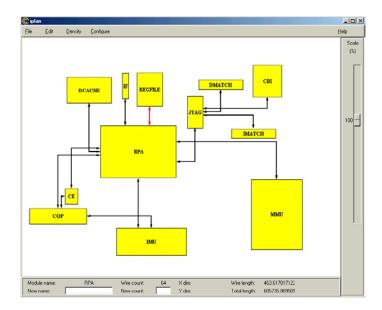

| 5.6  | IPLAN Interconnection Example (Lexra's LX4380)                                            | 87  |

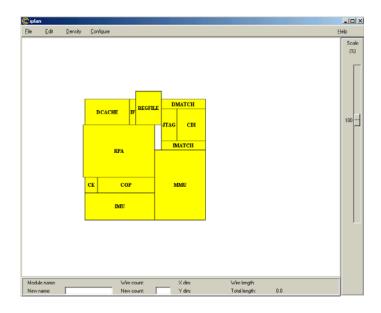

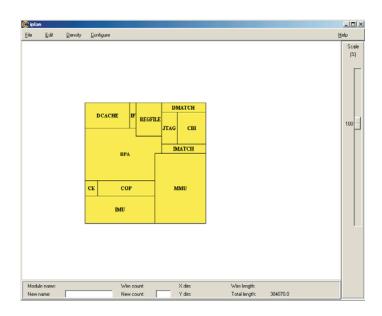

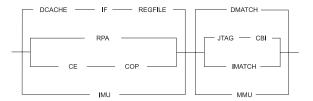

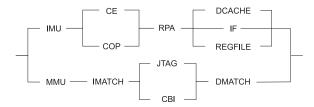

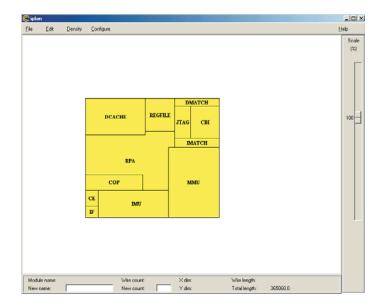

| 5.7  | LX4380's Floorplan after Optimizaton                                                      | 88  |

| 5.8  | LX4380's Floorplan after Optimization and Compaction                                      | 88  |

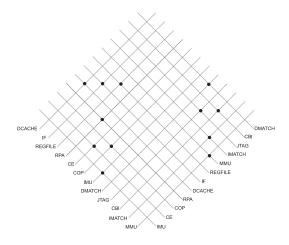

| 5.9  | Sequence Pair Representing LX4380's Floorplan                                             | 89  |

| 5.10 | Floorplan Horizontal Constraint Graph                                                     | 89  |

| 5.11 | Floorplan Vertical Constraint Graph                                                       | 89  |

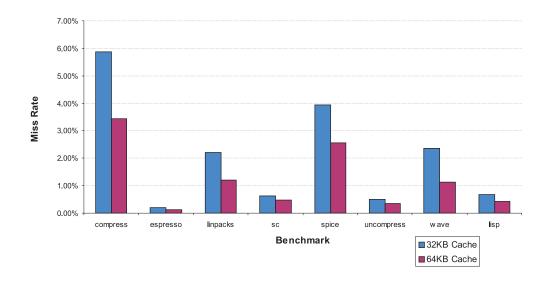

| 5.12 | Miss Rates with 32KB and 64KB Cache Sizes                                                 | 91  |

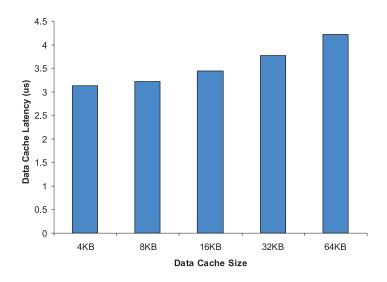

| 5.13 | Cache Latency vs Cache Size                                                               | 92  |

| 5.14 | Optimized Floorplan with a 64KB Data Cache                                                | 93  |

| 5.15 | Block Diagrams of Non-pipelined Cache and 2-Stage Pipelined Cache                         | 94  |

| 5.16 | Optimized Floorplan with Dual Issue                                                       | 96  |

| A.1  | Two chains of nodes connected at every node in a 1-D Manhattan grid                       | 103 |

| A.2  | Two chains of nodes connected at one end node in a 1-D Manhattan grid $$ .                | 104 |

| A.3  | Two chains of nodes connected at two end nodes in a 1-D Manhattan grid .                  | 104 |

| A.4  | $m \times n$ Rectangular Block                                                            | 105 |

| Δ 5  | I. Shaped Block                                                                           | 106 |

| A.6 | O-Shaped Block                                                             | 108 |

|-----|----------------------------------------------------------------------------|-----|

| A.7 | C-Shaped Block                                                             | 109 |

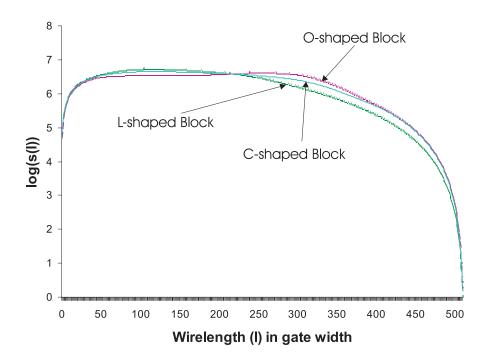

| A.8 | Structural Wirelength Distributions of an L-shaped block, a C-shaped block |     |

|     | and an O-shaped block (M = 256, N = 128)                                   | 110 |

## Chapter 1

## Introduction

#### 1.1 On-Chip Interconnect System

On-chip interconnect system is used for distributing clocks and power supplies, and connecting signals among circuits. Today digital integrated circuit (IC) is composed of transistors fabricated epitaxially on a lightly doped silicon substrate. Alternating dielectric and metal layers are grown on top of the transistors. The metal layers are typically made of copper (Cu), aluminum (Al) or tungsten (W), whereby the dielectric layers are made of silicon dioxide  $(SiO_2)$ . The state-of-the-art silicon chips may consist of eight or more metal layers  $(M_1 - M_8)$ , forming a three-dimensional interconnect structure (Figure 1.1) [Tai, Uni]. To minimize cross couplings between layers, all interconnections usually run in the same direction within a layer and perpendicularly between adjacent layers [She95].

Figure 1.1: Metal interconnect structure of a chip after etching of dielectric layers [ES00]

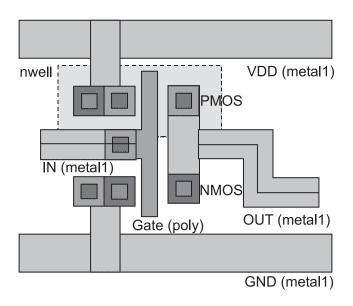

Figure 1.2 shows the layout diagram of a complementary metal-oxide-semiconductor field-effect transistor (CMOS) inverter. The pMOS transistor is located in an n-doped well, whereas the nMOS transistor is located in a p-doped substrate. In this example, the metal layer  $M_1$  is used for providing power supply and connecting the CMOS inverter input and output signals to the other circuits. Metal contacts, known as vias, connects the metal layer to the two transistor gates.

Figure 1.2: Topview of a CMOS Inverter Layout

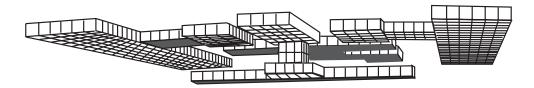

A three-dimensional (3-D) visualization of the interconnections is shown in Figure 1.3. It is tedious to precisely measure all interconnect characteristics, but researchers have developed approximation models extracting the vital interconnect parameters, such as capacitance and inductance, fairly accurately and efficiently [Bak90].

Figure 1.3: 3-D View of the Interconnections in a CMOS Inverter

On-chip interconnections can be broadly divided into the three categories:

- Local interconnections are intended for connecting transistors within a functional block. They usually use the minimum pitch to wire up large circuits at local level. These wires have relatively high resistivity and are typically driven by small transistors. Their maximum length scales with feature size and is around 1mm at 0.18  $\mu m$  feature size.

- Intermediate interconnections are for spanning large circuit blocks. They normally use a pitch and cross-sectional area greater than the minimum and have a maximum length of around 2-5mm. Unlike local interconnections, these wires do not scale with feature size.

- Global interconnections are for distributing power supply and for connecting data busses, control busses and clock signals. They are usually much less dense and have large cross-sectional area to minimize wire delay and power loss. These wires span the entire chip connecting separate functional blocks within the design.

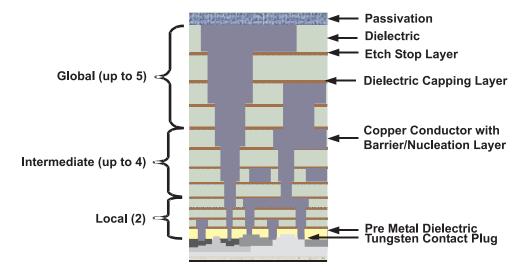

As feature size shrinks, the projected system-on-chip (SOC) die size remains roughly constant in the near future, incorporating more functionalities on a single chip [Ass01]. Thus, global and intermediate interconnection delays are increasingly more dominant relative to gate delays. Usually, the lower metal layers within smaller cross-sectional areas (e.g.  $M_1 - M_2$ ) are used for local interconnections, and the higher metal layers with larger cross-sectional areas (e.g.  $M_3 - M_8$ ) are reserved for intermediate and global interconnections. Figure 1.4 shows the cross-sectional view of these three types of interconnections in an integrated circuit.

#### 1.2 Deep Submicron Interconnect Issues

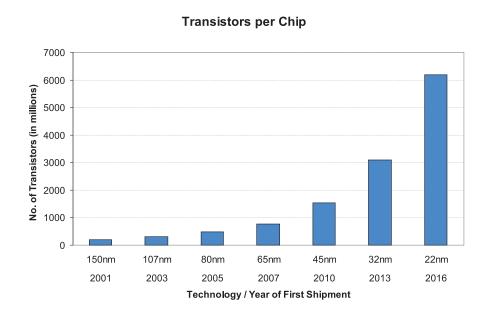

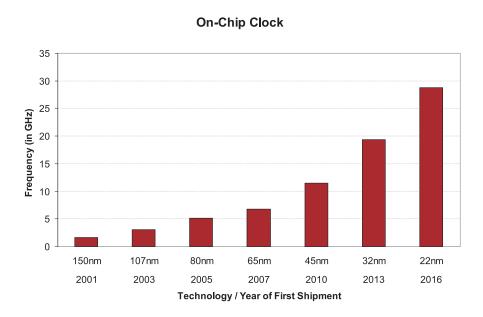

Deep submicron technology allows designers to build very complicated chips with hundreds of millions of very fast transistors. According to the Semiconductor Industries Association (SIA), the number of transistors and the clock frequencies for high performance microprocessors will continue to grow exponentially in the near future [Ass01] (Figures 1.5 and 1.6).

Figure 1.4: Cross-sectional View of the Interconnections in an IC

Figure 1.5: Total Transistors per Chip from 2001 to 2016

Figure 1.6: On-Chip Clock from 2001 to 2016

However, the interconnect properties do not scale with the feature size, thus limiting the usefulness of the vast number of fast transistors. This section discusses the issues related to the on-chip interconnect system, including performance, power consumption, reliability, manufacturing yield, and signal integrity.

#### 1.2.1 System Performance

Much improvement in chip performance has been due to technology scaling, allowing increased circuit densities at higher clock frequencies. As feature sizes shrink, device area shrinks roughly as the square of the scaling factor, and device delay improves approximately linearly with feature size. Unfortunately, interconnect delay does not scale with the feature size. When all three dimensions of an interconnect wire are scaled down by the same factor, the interconnect delay remains roughly unchanged. Consequently, interconnect delay becomes the performance bottleneck [FHR99].

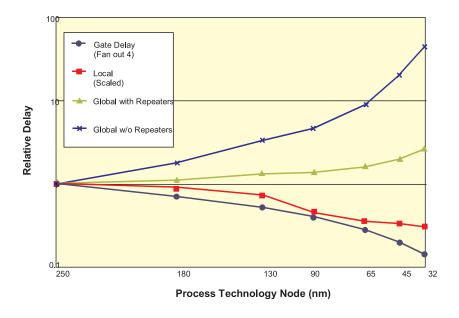

Systems today are integrated to upward of 10<sup>8</sup> devices per square centimeter. Interconnects — both within a single chip and across chip boundaries — determine the signal latency. Figure 1.7 shows the projections of gate and interconnect delays. While local interconnections scale roughly with the feature size, intermediate and global interconnections

certainly do not. This poses a major challenge in the future system-level design, implying that "interconnect-driven architectures" are becoming crucial.

Figure 1.7: Interconnect Delay

A related problem is the fact that the present CAD design tool cannot handle the exponential growth in the number of interconnections. Occasionally the physical synthesis tool cannot meet timing closure due to excessive interconnect delays caused by long wires. This timing closure problem is also known as "wire exceptions." The wire exceptions are a serious problem because they have to be fixed manually by adjusting physical placements or even changing the logic or architectural design. As feature size shrinks, the number of wire exceptions (following the number of wires) is expected to increase exponentially [Ron01], suggesting that a new system-level design methodology is becoming necessary.

#### 1.2.2 Power Dissipation

Power consumption has received much attention recently because of growing demands for wireless and portable electronic appliances. The three main sources of power dissipation in a CMOS circuit ( $P_{total}$ ) are the switching loss, the direct-path short-circuit current, and

the transistor leakage current, corresponding to the three terms in Equation 1.1 [CSB92].

$$P_{total} = p_t (C_L \cdot V \cdot V_{dd} \cdot f_{clk}) + I_{sc} \cdot V_{dd} + I_{leakage} \cdot V_{dd}$$

(1.1)

The first term  $p_t (C_L \cdot V \cdot V_{dd} \cdot f_{clk})$  represents the switching loss, in which  $C_L$  is the sum of the interconnect and gate capacitances,  $V_{dd}$  is the supply voltage, V is the voltage swing,  $f_{clk}$  is the clock frequency, and  $p_t$  is the transition probability. In most CMOS design, the voltage swing V and the supply voltage  $V_{dd}$  are identical. The second term  $I_{sc} \cdot V_{dd}$  represents the short-circuit power loss, in which  $I_{sc}$  is the short-circuit current. The third term  $I_{leakage} \cdot V_{dd}$  represents the loss caused by leakage current, in which  $I_{leakage}$  is the CMOS leakage current.

Among all these terms, interconnect switching loss represents the most important power loss in deep submicron design. In general, the interconnect switching loss may be mitigated by lowering (or dynamically adjusting) supply voltage, switching frequency, or by reducing interconnect capacitance. At the architectural design phase, there is a tradeoff among area, system performance and power consumption [FHR99]. For instance, multiple functional units running in parallel at a sub-threshold voltage level can achieve the same performance as a single functional unit running at a nominal voltage but effectively consume much less power [Bha94]. At the physical design phase, power consumption can be reduced by minimizing interconnect wirelength and wire congestion using different floorplan or different placement and routing algorithms.

#### 1.2.3 Reliability and Manufacturing Yield

Interconnect affects chip reliability and manufacturing yield in a variety of ways, such as process-induced damage, electromigration, and bridging defects caused by particle contamination. As feature size shrinks, long interconnect can create excessive static charge buildup at the gate during the ion and plasma implant processes, causing permanent damages to the gate oxide. This is known as process-induced damage [GM92]. For a given manufacturing process, a process-induced damage rule (also known as antenna rule) is used to define the maximum ratio of interconnect area to transistor gate area.

Electromigration is caused by the excessive transport of the metal atoms when an electric current flows through an on-chip interconnection for a prolonged period of time [Bla69]. Aluminum is especially vulnerable to electromigration due to its low melting point. The

problem can be alleviated by adding alloy elements (e.g. copper), blocking the grain boundary diffusion path. Another related problem is the migration of silicon into aluminum at the metal contacts, known as *contact electromigration*, which arises when the silicon atoms diffuse into aluminum at the interface area where the void created by the migrating silicon is filled by aluminum. In general, both reliability and manufacturing yield decreases with longer interconnection and with higher current density. Recently, researchers have developed models predicting the manufacturing yield based on the interconnect wirelength estimation and layer assignment [CdG01]. The manufacturing yield estimation function may also be used in the CAD tools to drive the physical layout [Isr00].

#### 1.2.4 Signal Integrity

In the past chip designers could tape out designs without bothering with signal integrity closure. However, skipping signal integrity analysis is no longer an option below 0.13-micron process [Pol]. As the design shrinks, the reduced wire spacing results in larger interconnect cross-sectional aspect ratio. Consequently, the cross-capacitance and cross-inductance between neighboring wires would create more coupling noise, significantly undermining the signal integrity. As CMOS gates are voltage driven, when the coupling noise caused by the aggressor wire exceeds the noise margin in the victim circuit, the entire system becomes unreliable.

Signal integrity can be improved by increasing wire spacing or by adding ground wires between adjacent signals. Nevertheless, these techniques cannot be used in congested routing areas because there is no room to increase wire spacing or to add ground wires. Hence, it is important to spread the wire density evenly as much as possible to avoid congestion hotspots.

#### 1.3 Our Work

#### 1.3.1 Motivation

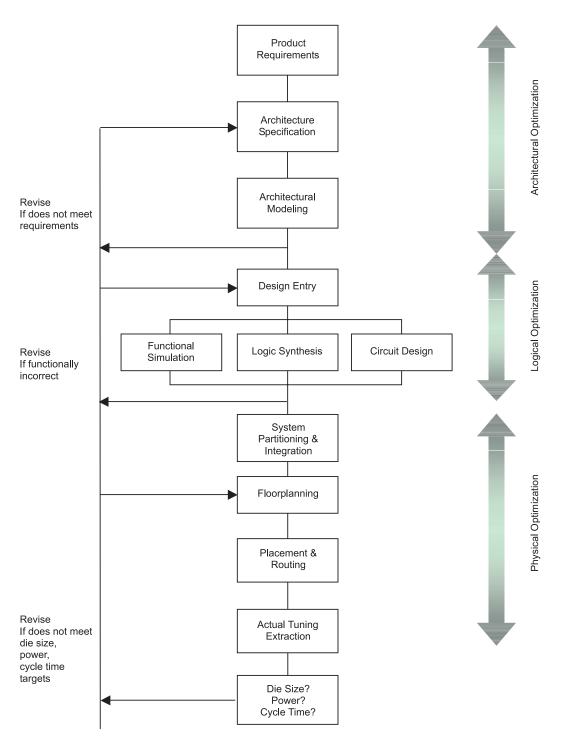

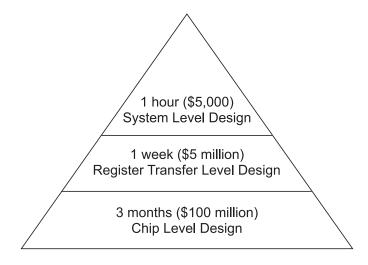

In the traditional VLSI design flow, there are three separate and distinct optimization phases: architectural optimization, logic optimization and physical optimization (Figure 1.8).

Figure 1.8: Traditional Design Flow

A VLSI design project starts from the architectural design phase, then proceeds to the logic and circuit design phase, and finally to the physical design phase. If design specifications or requirements cannot be met at some point, the project may need to roll back to the previous design phase.

This style of design methodology is analogous to the waterfall model in software design, where requirements analysis, architectural design, detailed design, coding, testing and integration are separated into distinct phases [Roy70]. The software waterfall model is risky in a large and complicated project because it does not sufficiently examine the design details in the early development cycle. As a result, design problems are sometimes uncovered only in the implementation phase when any major changes are extremely costly [Ber97]. In fact, the waterfall model has already been replaced by the rapid prototyping model and other related models, in which programmers build quick prototypes to minimize design risks [Gom83].

Similarly, it is also much cheaper to make changes in a VLSI design in the early design phases. As the design progresses, the costs and lost revenues associated with a major redesign increases exponentially (Figure 1.9). Sometimes late changes are so costly that the entire market opportunity window is lost. To avoid costly and time-consuming chip redesign, it is becoming crucial to obtain an accurate estimate of performance, cost and power consumption in the early design stages and apply these estimates to avoid expensive redesign later on [FH01].

Figure 1.9: Lost Revenue

#### 1.3.2 A Priori Interconnect Models

In this research, we propose an interconnect-driven floorplanning framework, in which designers can build fairly accurate prototypes evaluating system cost, performance, power consumption and other design parameters. As interconnect is becoming the pre-dominant factor in determining all these design parameters, we have developed models to characterize the interconnect properties and examined their architectural impacts.

We have developed three statistical, a priori models — a wirelength distribution model, a wire congestion model and a processor performance model — in our study. Our wirelength distribution model is an extension to the Davis' model [DDM96], whereas our proposed wire congestion model and interconnect-driven processor performance model are derived based on probability theory. The details of these three models are discussed in Chapters 2, 3 and 4, respectively.

An inherent limitation of statistical models is that while these models may accurately predict interconnect properties (e.g. wirelength) for the majority of the wires, they inevitably over-estimate or under-estimate interconnect properties for some of the wires. This is probably unavoidable due to the lack of information in the early design stages. As design progresses, on-line and a posteriori interconnect models can be used in conjunction with a priori interconnect models to improve modeling accuracy [Str99].

#### 1.4 Organization of this Dissertation

- Chapter 1 introduces the effects of interconnect in deep-submicron era and discusses our research objectives.

- Chapter 2 presents a generalized wirelength distribution model.

- Chapter 3 presents an interconnect congestion model and describes a floorplan algorithm that uses the congestion model.

- Chapter 4 presents a processor performance model that takes interconnect overhead into consideration. An upper bound on the optimum issue width (based on interconnect overhead) is described and derived in this chapter.

- Chapter 5 introduces the IPLAN floorplanning framework, which incorporates the interconnect models described in the previous chapters as well as a number of design

tools previously developed in our research group. A case study using Lexra LX4380 is presented to show how the floorplanning framework works.

- Chapter 6 presents the conclusions and discusses about the future work.

- Appendix A shows the derivations of some structural wirelength distributions discussed in Chapter 2.

## Chapter 2

## Wirelength Distribution Model

Interconnect wirelength is the most important parameter in determining interconnect delay, power loss, reliability and signal integrity. By examining the wirelength distribution of design alternatives, chip designers can more effectively perform architectural tradeoffs, taking the effects of interconnections into consideration [HF00]. This chapter introduces a wirelength distribution model, which is one of the three interconnect models used in the IPLAN floorplanning framework [HSF01].

#### 2.1 Introduction

This introduction section provides the background of the wirelength models developed by other researchers. Sutherland and Oestreicher [SO72] were the first researchers to determine an upper bound of interconnect wirelengths. However, their estimates were overly pessimistic because their model was based on a pure random placement. However, connected blocks are usually placed in close proximity by commercial place-and-route tools. Donath [Don79, Don81] used Rent's Rule [LR71] to derive a tighter upper bound on the expected interconnect wirelength based on a two-dimensional hierarchical placement. Using a similar approach, Masaki and Yamada [MY87] derived the expected interconnect wirelengths for various 2-D and 3-D system packaging structures. Sastry and Parker [SP86] showed that the wirelength distribution in gate arrays follows a Weibull distribution. Later, Gura and Abraham [GA89], Pedram and Preas [PP89], and Stroobandt [Str96] modified and further enhanced the model.

Recently, Davis et al. [DDM98] constructed a wirelength distribution model based on a

non-hierarchical placement. This model is significant because it shows that the wirelength distribution can be derived without explicitly using hierarchical partitioning. Furthermore, the wirelength distribution appears to be more accurate than the previous models for long wires. In our research, we extend Davis' model to investigate the effects of aspect ratio and routing obstacles on interconnect wirelength.

The number of terminals (T) and the number of gates (N) in a VLSI design are related by a simple empirical formula, known as Rent's Rule [LR71].

$$T = kN^p (2.1)$$

In this equation, k is the average number of terminals per gate and p is the Rent's constant. The Rent's constant can be determined empirically and is found to be between 0.5 and 0.75 [Bak90]. Davis et al. investigated a square array of N gates with  $\sqrt{N}$  rows and  $\sqrt{N}$  columns. The horizontal and vertical gate pitches are both equal to one unit, so the aspect ratio of the entire array is one. A continuous interconnect density function i(l) is defined such that the number of interconnects of length between l=a and l=b is:

$$\int_{a}^{b} i(l)dl \tag{2.2}$$

The continuous interconnect density function i(l) consists of three components: a gate pair structural distribution function M(l), a gate pair connection probability  $I_{exp}(l)$ , and a normalization factor  $\Gamma$ .

$$i(l) = \Gamma M(l)I_{exp}(l) \tag{2.3}$$

The gate pair structural distribution function M(l) can be found by inspection [DDM98], or more easily by using moment generating polynomials [Str96].

$$M(l) = \begin{cases} \frac{l^3}{3} - 2\sqrt{N}l^2 + 2Nl & \text{if } 1 \le l \le \sqrt{N} \\ \frac{(2\sqrt{N} - l)^3}{3} & \text{if } \sqrt{N} \le l \le 2\sqrt{N} \\ 0 & \text{otherwise} \end{cases}$$

(2.4)

Based on Rent's Rule, Feuer [Feu82] showed that the gate pair connection probability  $I_{exp}(l)$  in a two-dimensional array is proportional to  $l^{2p-4}$ . The same result was also derived by Davis et al. [DDM98]. According to Donath [Don79], the total number of interconnects

is  $\alpha k N(1-N^{p-1})$ . The constant factor  $\alpha$  is equal to f/(f+1), where f is the average fanout of the system. The normalization factor  $\Gamma$  can be found by integrating i(l) over the entire range of wirelength.

$$\Gamma = \frac{\alpha k N (1 - N^{p-1})}{\int_{1}^{2\sqrt{N}} M(l) l^{2p-4} dl}$$

(2.5)

Davis' model assumes a square array of gates, but in practice many blocks cannot be designed and placed with unity aspect ratio. Moreover, there can be many routing obstacles in real designs. It is therefore useful to investigate the effects of aspect ratio and routing obstacles on wirelength distribution. Furthermore, the horizontal and vertical gate pitches can be very different, and it would be useful to examine the effects of the gate pitches.

#### 2.2 Wirelength Distribution Model for Rectilinear Blocks

#### 2.2.1 Effects of Block Aspect Ratio

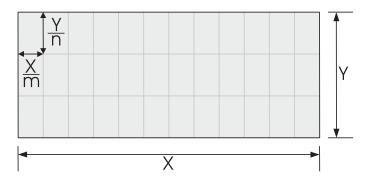

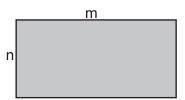

Consider a rectangular block with m columns and n rows. The total number of gates is  $N=m\times n$ , and the dimensions of the entire block are X and Y units. Hence, the horizontal gate pitch is  $\frac{X}{m}$  units, the vertical gate pitch is  $\frac{Y}{n}$  units, and the average gate pitch  $\lambda$  is  $\sqrt{\frac{XY}{N}}$  units. Without loss of generality, we assume  $X\geq Y$ .

Figure 2.1: Rectangular array of  $m \times n$  gates

We follow a similar approach as described in the previous section. We first derive the structural distribution function M(l) and then calculate the gate pair connection probability  $I_{exp}(l)$ . For each row of gates, we define the horizontal discrete structural distribution

function  $M_x(l)$  to be the number of gate pairs with distance l. It can be found by inspection [Str96].

$$M_x(l) = \begin{cases} m & \text{if } l = 0\\ \frac{2m(X-l)}{X} & \text{if } \frac{X}{m} \le l \le X\\ 0 & \text{otherwise} \end{cases}$$

(2.6)

Similarly, for each column of gates, we can define the vertical discrete structural distribution function  $M_y(l)$ . The expression is similar to  $M_x(l)$ .

$$M_{y}(l) = \begin{cases} n & \text{if } l = 0\\ \frac{2n(Y-l)}{Y} & \text{if } \frac{Y}{n} \le l \le Y\\ 0 & \text{otherwise} \end{cases}$$

(2.7)

Since m and n are large numbers, we can approximate these discrete structural distribution functions to be continuous. The continuous distribution functions are realistic because the I/O ports may be located anywhere in the gates and the interconnect wirelengths are usually not equal to multiples of the gate pitches. The continuous structural distribution function M(l) is simply the convolution of  $M_x(l)$  and  $M_y(l)$ . To simplify the expression of M(l), we add a constant scaling factor XY/2N. This constant is later absorbed in the normalization factor  $\Gamma$ .

$$M(l) = \frac{XY}{2N} \int_{0}^{l} M_{x}(x) M_{y}(l-x) dx$$

(2.8)

Evaluating the definite integral from x = 0 to x = l, we get the following expression for M(l).

$$M(l) = \begin{cases} \frac{l^3}{3} - (X+Y)l^2 + 2XYl & \text{if } l \le Y \\ -Y^2l + XY^2 + \frac{Y^3}{3} & \text{if } Y \le l \le X \\ \frac{(X+Y-l)^3}{3} & \text{if } X \le l \le X + Y \\ 0 & \text{otherwise} \end{cases}$$

(2.9)

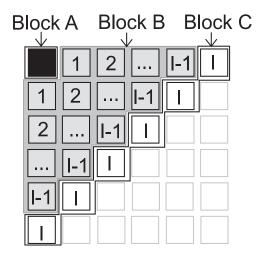

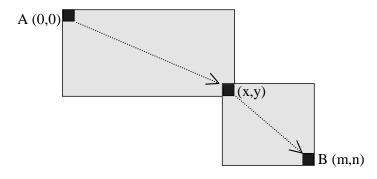

The gate pair connection probability  $I_{exp}(l)$  is the expected number of interconnections between a pair of gates that are l units apart. In order to calculate  $I_{exp}(l)$ , we follow Davis' approach and define block A, block B, and block C, as shown in Figure 2. In general, the horizontal and vertical gate pitches do not have to be identical, but they are shown to be the same in the diagram. Block A represents a single gate in the rectangular array; block C consists of all the gates with a distance l away from block A; block B consists of all the gates between block A and block C.

Figure 2.2: Definitions of Blocks A, B, and C

$N_A$ ,  $N_B$ , and  $N_C$  are the number of gates in block A, B, and C, respectively. Using Rent's Rule,  $I_{exp}(l)$  can be determined as below [DDM98].

$$I_{exp}(l) \cdot N_C = k((N_A + N_B)^p + (N_B + N_C)^p - N_B^p - (N_A + N_B + N_C)^p)$$

(2.10)

The number of gates in block A  $(N_A)$  is always 1. For short interconnects  $(l \leq Y)$ ,  $N_B$  is proportional to  $l^2$  and  $N_C$  is proportional to l. For longer interconnects  $(l \geq Y)$ ,  $N_B$  is approximately proportional to l instead of  $l^2$  and  $N_C$  is approximately a constant. Using binomial expansion,  $I_{exp}(l)$  is proportional to  $l^{2p-4}$  for short interconnects and  $l^{p-2}$  for longer interconnects. Thus, i(l) can be determined by the following equation.

$$i(l) = \begin{cases} \Gamma M(l)l^{2p-4} & \text{if } l \leq Y\\ \Gamma M(l)(Y \cdot l)^{p-2} & \text{if } Y \leq l \leq X + Y\\ 0 & \text{otherwise} \end{cases}$$

(2.11)

For  $Y \leq l \leq X + Y$ , a scaling factor  $Y^{p-2}$  is added to ensure that  $I_{exp}(l)$  is continuous at l = Y. As before, the normalization factor  $\Gamma$  can be found by integrating i(l) over the

entire range.

$$\Gamma = \frac{\alpha k N (1 - N^{p-1})}{\int_{\lambda}^{Y} M(l) l^{2p-4} dl + \int_{Y}^{X+Y} M(l) (Y \cdot l)^{p-2} dl}$$

(2.12)

Please note that the interconnect density function i(l) does not depend on the gate aspect ratio. Equations 2.9 and 2.11 show that the wire distribution function has three distinct regions: (a) short wires  $(l \leq Y)$ , (b) medium wires  $(Y \leq l \leq X)$ , and (c) long wires  $(X \leq l)$ . If  $X = Y = \sqrt{N}$  units (one unit is equal to one gate pitch), there is no medium wire, and our model is similar to Davis' model. The only difference is that  $I_{exp}(l)$  is equal to  $(Y \cdot l)^{p-2}$  instead of  $l^{2p-4}$  for long wires. However, the two models are quite different for non-unity aspect ratios. In particular, the average wirelength estimations are very different. The average wirelength  $l_{av}$  is derived in Equation 2.13.

$$l_{av} = \frac{\int_{\lambda}^{X+Y} i(l) \cdot l \, dl}{\int_{\lambda}^{X+Y} i(l) \, dl}$$

$$= \frac{\int_{\lambda}^{Y} M(l) l^{2p-3} \, dl + \int_{Y}^{X+Y} M(l) (Y \cdot l)^{p-2} \cdot l \, dl}{\int_{\lambda}^{Y} M(l) l^{2p-4} \, dl + \int_{Y}^{X+Y} M(l) (Y \cdot l)^{p-2} \, dl}$$

(2.13)

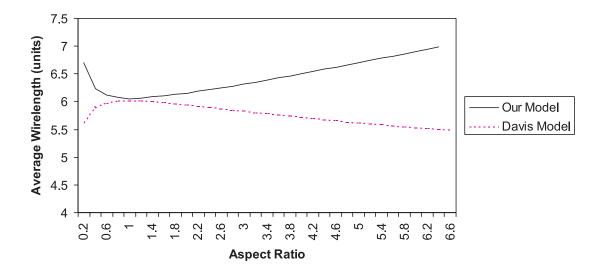

If we assume that  $I_{exp}(l)$  is equal to  $l^{2p-4}$  for all wires (as in Davis' model), the estimated average wirelength estimate decreases with higher aspect ratios. This is incorrect as it contradicts with our experimental results. On the other hand, we set  $I_{exp}(l)$  to be  $l^{2p-4}$  for short wires and  $l^{p-2}$  for medium and long wires in our model. There are relatively more long wires in our model and the average wirelength increases almost linearly with the aspect ratio.

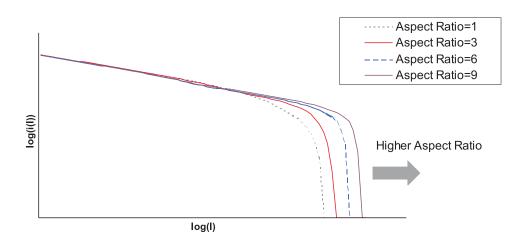

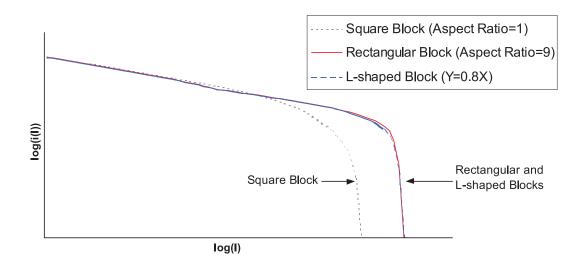

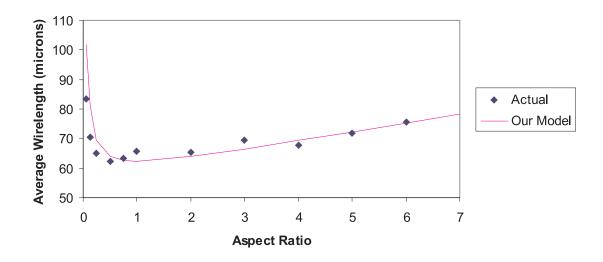

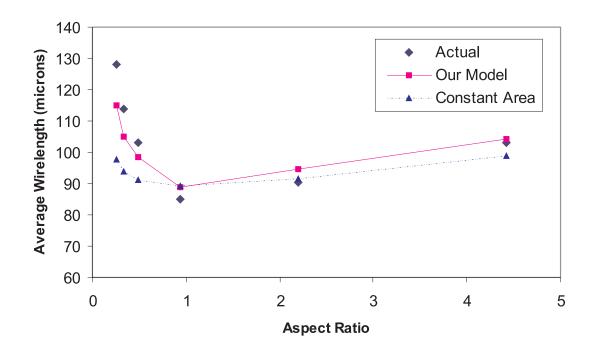

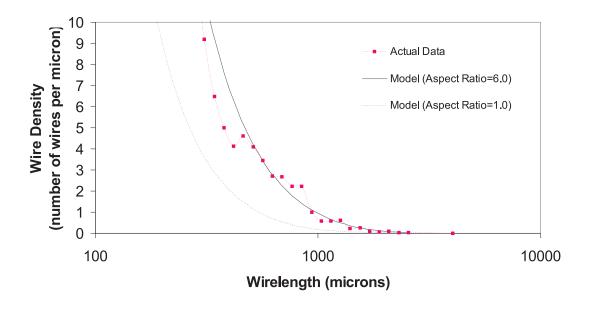

Figure 2.3 compares the average wirelength estimates derived from both models. In this graph, p is 0.67,  $\lambda$  is one unit, and the total area is 10,000 square units. Assume that the area of the rectangular block is fixed. Figure 2.4 shows the theoretical wirelength distributions of the block with various aspect ratios. As before, the Rent's constant p is set to 0.67.

For short wires, the slope of the log-log graph is roughly equal to 2p-3 (or -1.66) because M(l) is roughly proportional to l (according to Equation 2.9) and  $I_{exp}(l)$  is proportional to  $l^{2p-4}$ . Similarly for medium wires, the slope is roughly equal to p-2 (or -1.33) because M(l) is roughly constant and  $I_{exp}(l)$  is proportional to  $l^{p-2}$ . For p=0.67, the two slopes are quite similar and the two regions may not be very distinctive in the graph. The distribution

Figure 2.3: Average Wirelength Estimations vs Aspect Ratio

tails off when the wirelength is near X + Y.

It is apparent that rectangular blocks with higher aspect ratios contain more long wires, but the wire density function i(l) for short wires remains roughly the same. The number of short wires far exceeds the number of long wires, and the small increase in the number of the long wire does not substantially affect the wire distribution of the short wires.

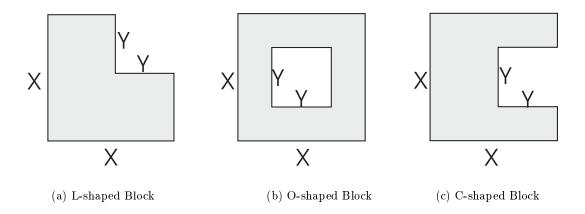

#### 2.2.2 Effects of Routing Obstacles

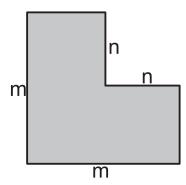

The effects of routing obstacles on interconnect wirelength are similar to the effects of aspect ratio. Routing obstacles spread out connected gates and may cause some long interconnections. As in the case of high aspect ratios, obstacles are expected to increase the number of long wires without significantly affecting the number of short wires. Figure 2.5 shows three simple routing obstacle examples. In Figure 2.5(a), the routing obstacle is located at the corner of the block; in Figure 2.5(b), the obstacle is located inside the block; in Figure 2.5(c), the obstacle is located on the edge of the block.

First, we examine the L-shaped block in Figure 2.5(a). The structural distribution function M(l) shown in Table 2.1 may be derived using the moment generating polynomial technique (Appendix A). The gate pair connection probability  $I_{exp}(l)$  is derived as shown in the previous section.  $I_{exp}(l)$  is proportional to  $l^{2p-4}$  for short wires  $(l \leq X - Y)$  and is

Figure 2.4: Wire Density Function i(l) for Various Aspect Ratios

proportional to  $l^{p-2}$  for long wires  $(l \geq X - Y)$ . The normalization factor  $\Gamma$  can be found by integrating i(l) from  $\lambda$  to 2X.

Table 2.1: Structural Length Distribution Function for the L-shaped Block<sup>1</sup>

| Wirelength $(l)$         | $M\left(l ight)$ for the L-shaped Block                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| $l \leq X - Y$           | $\frac{1}{2}l^3 - 2Xl^2 + \frac{4X^2 - 4Y^2 - 1}{2}l$                                                                   |

| $X - Y \le l \le Y$      | $\frac{1}{6}l^3 - (X-Y)l^2 + \frac{6X^2 - 12XY + 6Y^2 - 1}{6}l + \frac{X^3 - X + Y + 3X^2Y - 9XY^2 + 5Y^3}{3}$          |

| $Y \le l \le 2X - 2Y$    | $-\frac{1}{6}l^3 + (2Y - X)l^2 + \frac{6X^2 - 12XY + 1}{6}l + \frac{X^3 - X + 3X^2Y - 9XY^2 + 6Y^3}{3}$                 |

| $2X - 2Y \le l \le X$    | $-\frac{1}{3}l^3 + Yl^2 + \frac{6XY - 3X^2 - 6Y^2 + 1}{3}l + \frac{5X^3 - 2X + Y - 9X^2Y + 3XY^2 + 2Y^3}{3}$            |

| $X \le l \le 2Y$         | $-\frac{1}{3}l^3 + (2X - Y)l^2 + \frac{18XY - 15X^2 - 6Y^2 + 1}{3}l + \frac{11X^3 - 2X + Y - 15X^2Y + 3XY^2 + 2Y^3}{3}$ |

| $2Y \le l \le 2X - Y$    | $-\frac{3}{6}l^3 + 2(X-Y)l^2 + \frac{36XY - 30X^2 + 1}{6}l + \frac{11X^3 - 2X + 2Y - 15X^2Y + 3XY^2 - 2Y^3}{3}$         |

| $2X - Y \le l \le X + Y$ | $\frac{1}{6}l^3 - Yl^2 + \frac{12XY - 6X^2 + 6Y^2 - 1}{6}l + \frac{3X^3 + Y - 3X^2Y - 3XY^2 - Y^3}{3}$                  |

| $X + Y \le l \le 2X$     | $-\frac{l^3}{6} + Xl^2 - 2X^2l + \frac{8X^3 - 2X + 1}{6}$                                                               |

<sup>&</sup>lt;sup>1</sup>We assume X < 2Y in this table.

As the expression of the wire distribution is quite complicated, we would like to approximate the L-shaped block by a rectangular block for interconnect wirelength estimation so that the wirelength distribution can be more easily calculated in software by the CAD tools. First, we examine the wire distribution of an L-shaped block and compare the L-shaped block with a rectangular block of the same area  $(X^2 - Y^2)$ . In order to match the longest

Figure 2.5: Routing Obstacle Examples

wirelengths in these two blocks ( $l_{max} = 2X$ ), the aspect ratio of the rectangular block is set to  $\frac{X+Y}{X-Y}$ . Figure 2.6 compares the two wirelength distributions and shows that the two distributions are almost identical. For long wires ( $l \approx 2X$ ), the wire density function i(l) of the rectangular block is twice the wire density function of the L-shaped block. This is because there are two "diagonals" in the rectangular block, and the connections across these two "diagonals" can both constitute long wires. On the other hand, there is only one long "diagonal" in the L-shaped block.

Likewise, we can derive the wirelength distribution functions of the O-shaped block in Figure 2.5(b) and the C-shaped block in Figure 2.5(c). The derivations are shown in Appendix A. For  $Y \leq X/2$ , the theoretical wirelength distributions of these two blocks are both very similar to the L-shaped block. As in the rectangular block, the numbers of long wires  $(l \approx 2X)$  in the O-shaped and C-shaped blocks are about twice the number of long wires in the L-shaped block because there are two long "diagonals" in the O-shaped and C-shaped blocks. For Y > X/2, the maximum wirelength in C-shaped block is equal to X + 2Y, which is longer than the maximum wirelengths in the L-shaped and O-shaped blocks. In general, it is better to place routing obstacles near the corner in order to reduce the number of long wires.

#### 2.3 Experimental Results

Our model was verified with some previously published data and three other design examples. The three design examples are Cordic, Multiplier, and IDCT.

Figure 2.6: Wirelength Distributions of L-shaped and Rectangular Blocks

Table 2.2: Experimental Results on Average Wirelength Estimation

| Design     | No. of | No. of | Р    | Area in $mm^2$     |

|------------|--------|--------|------|--------------------|

|            | gates  | conns  |      | for aspect ratio=1 |

| Cordic     | 2151   | 3384   | 0.75 | 0.28               |

| Multiplier | 6367   | 16050  | 0.72 | 1.3                |

| IDCT       | 12666  | 35193  | 0.63 | 4.2                |

The Multiplier and Cordic designs were synthesized using Synopsys Design Compiler, and the IDCT design was synthesized using Synopsys Behavioral Compiler. The netlists of these designs were generated for TSMC  $0.35\mu m$  technology. The floorplanning, placement, and routing of the designs were performed by Epoch from Duet Technologies, and the wirelength extractions were done by Cadence Dracula. In this section, we first investigate the average wirelength and then examine the wirelength distribution.

#### 2.3.1 Average Wirelength Model

Our average wirelength estimates were derived from Equation 2.13, and were then compared with Donath's estimates [Don79] using the experimental data cited in his paper. In Donath's experimental data, the aspect ratios of his blocks are all approximately one. The results

are shown in Table 2.3. Although our estimates are still higher than the actual data, they are substantially more accurate than Donath's estimates. For example in Graph B, the estimation error is reduced by about half. Since the aspect ratios are close to one, our estimated average wirelengths are similar to Davis' model. We also compared our average wirelength estimation with Stroobandt's model [Str96] and the two results are comparable. Our estimation is better in Graphs C and F, and worse in Graphs B, D, and E (Graph A is not available in [Str96]).

Graph No. of No. of Donath's Stroobandt's Our Actual p gates conns formula estimate estimate length 60 100 0.67 2.76 \_\_\_ 2.28 1.29 Α 4.02 2.88 2.15 В 528 1007 0.59 3.09 С 576 1111 0.75 5.26 4.13 3.92 2.85 D 671 1670 0.57 4.07 2.89 3.13 2.63 1239 3.76 2.45 2.97 Ε 2687 0.47 2.14 F 2148 7302 0.75 7.37 5.74 5.29 3.50

Table 2.3: Experimental Results on Average Wirelength Estimation

Next, we compare the theoretical average wirelength with the actual average wirelength in the *Cordic* design for a number of aspect ratios. We calculate the wirelength density function and determine from the slope of the function that the Rent's exponent p is around 0.72. As shown in Figure 2.7, the theoretical results closely match the actual data for a wide range of aspect ratios. The average wirelength increases when the aspect ratio increases, and the slope of the graph is around  $2.5 \mu m$ .

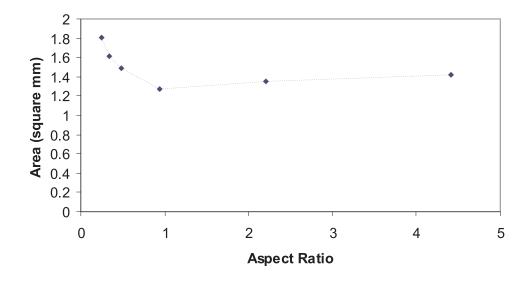

We did the same comparison for *Multiplier*, and the results are shown in Figure 2.8. The theoretical results are also close to the actual data. However, if we assume the total area of the block is fixed and then use the aspect ratio to estimate the average wirelength, the estimates are not as accurate (Figure 2.8). The reason is that the area of *Multiplier* changes considerably with different aspect ratios (Figure 2.9), which is different from the *Cordic* example in which the area remains roughly constant from 0.25 aspect ratio to 6.0 aspect ratio.

Figure 2.7: Average Wirelength vs Aspect Ratio (Cordic)

Figure 2.8: Average Wirelength vs Aspect Ratio (Multiplier)

Figure 2.9: Area vs Aspect Ratio (Multiplier)

## 2.3.2 Wirelength Distribution Model

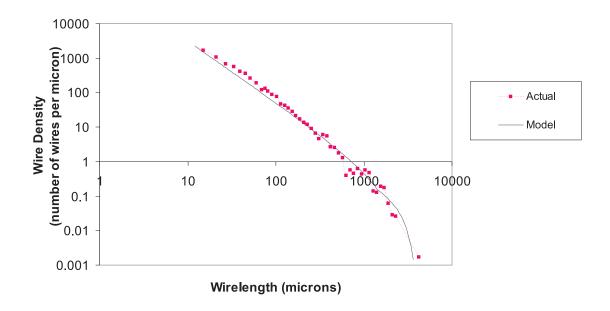

In this section, we examine the effects of aspect ratio and routing obstacles on wiring distribution. In order to calculate the wirelength density of a design, we need to construct a histogram of all wirelengths. Since the number of short wires is substantially higher than the number of long wires, it is sensible to have larger histogram bins for long wires and smaller histogram bins for short wires. Thus, our histograms are constructed in logarithmic scale. If a certain histogram bin contains no wire, this bin is then merged with an adjacent bin and the wire density is distributed evenly between the two bins. This is to reduce the number of bins and minimize the noise effects when the number of wires in a bin is too small.

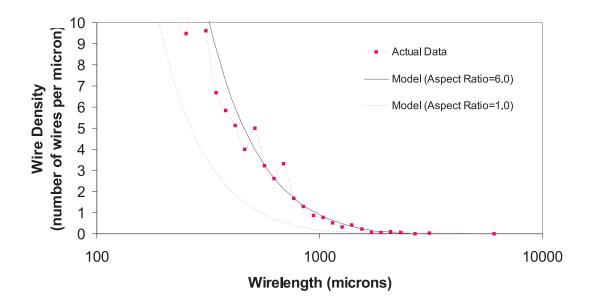

Figure 2.10 shows the wirelength distribution of IDCT with unity aspect ratio. Our theoretical wire density is similar to Davis' model, and it describes the actual wire density accurately. We change the aspect ratio of IDCT and measure the new wire density function. The general shape of the graph is same as before, but the number of long wires increases. The wire density is displayed in Figure 2.11. We also show the previous theoretical wire density in the same graph for comparison. To highlight the differences between the two

Figure 2.10: Wirelength Distribution with Unity Aspect Ratio (IDCT)

density functions near  $1000\mu m$ , the graph is drawn in semi-log scale instead of log-log scale. Similarly, we add a routing obstacle in IDCT to make it an L-shaped block, as in Figure 2.5(a). The X and Y dimensions are approximately 3.2mm and 2.3mm, respectively. As discussed in the previous section, the wire density can be approximated by a rectangular block with aspect ratio  $\approx 6$ . Figure 2.12 shows the wire density of the L-shaped block. We also add the previous two theoretical wire densities (aspect ratio=1, and aspect ratio=6) for comparison. As expected, the wire densities in Figure 2.11 and 2.12 are very similar.

Figure 2.11: Wirelength Distribution with Aspect Ratio = 6.0 (IDCT)

Figure 2.12: Wirelength Distribution with Routing Obstacles (IDCT)

# 2.4 Summary

This chapter presents a generalized interconnect wirelength distribution model and investigates the effects of aspect ratio and routing obstacles on interconnect wirelength. This model is important because interconnect wirelength is the most important parameter in determining the performance and power consumption of a chip in deep submicron design. The wirelength distribution (Equation 2.11) is divided into three wirelength regions: short wires  $(l \leq Y)$ , medium wires  $(Y \leq l \leq X)$ , and long wires  $(X \leq l)$  where l is the wirelength, X and Y are the width and height of the rectangular block. As described in Chapter 1, long wires can affect chip performance and cause wire exceptions during physical synthesis process. On the other hand, the power consumption is usually determined by the average wirelength (or total wirelength).

The wirelength distribution depends primarily on the Rent's exponent, the dimensions of the blocks, and the total number of gates in the block. To the first order approximation, the wirelength distribution is not sensitive to the number of rows or columns of gates in the block, or the aspect ratios of the gates. In order to accurately model the wirelength distribution, we determine that it is also important to estimate the effects of aspect ratios on the synthesized area. The area is usually smaller with unity aspect ratio, but the precise effects depend on the type of synthesized block, the synthesis tool and the cell library used. In general, these effects appear to be more serious for a datapath than for a controller block. As shown in the *Multiplier* example, if the changes in the synthesized area are not taken into consideration, the wirelength distribution results can be inaccurate when the aspect ratio is not unity. This is because the size of a datapath can be significantly larger when it is synthesized into an "inefficient" aspect ratio.

# Chapter 3

# Wire Congestion Model

Besides long interconnections, wire congestion is another main contributor of excessive wire delay and power loss. This chapter introduces a generalized statistical wire congestion model and a heuristic floorplanning algorithm that minimizes the wirelength and congestion in a floorplan [HF99]. The wire congestion model is described in Section 3.2, while the floorplanning algorithm is described in Section 3.3.

# 3.1 Introduction

As feature size shrinks, wires are becoming narrower and are placed closer to one another. At the same time, they are also becoming taller in order to reduce resistivity. The net outcome is that the coupling effects between neighboring wires (due to cross-capacitance and cross-inductance) are rising. To avoid excessive coupling, critical wires have to be placed farther apart or be shielded with ground wires [Naf99]. Nevertheless, this would not be possible when routing channels in a floorplan are already overly congested. Thus, interconnect congestion affects not only routability but also the area, performance, power consumption, and signal integrity of a design.

Congestion may be a global measure, such as excessive nets crossing a cutline between two partitions, or a local measure when the track density is too high within a routing channel. Congestion based algorithms have proved effective in global routing [Nai87, HS90, LSW94] and global placement [PBS98], in reducing total chip area, improving wireability, and predicting total wire length in the early design stages. In a typical placement tool, congestion is modeled by a rat's nest [She95] or similar connectivity visualizations [Leb83].

For simplicity, these congestion visualization schemes do not model via minimization [Hsu83, NMN87, RKN89] and routing obstacles. As a result, they may under-estimate routing congestion in some regions and over-estimate routing congestion in some other regions.

# 3.2 Wire Congestion Model

#### 3.2.1 Problem Formulation

#### Simplified Congestion Model

In the simplified congestion model, a chip layout is modeled by a grid graph [She95]. The grid graph G = (V, E) contains vertex at each grid point as well as horizontal and vertical edges connecting adjacent vertices. The horizontal and vertical spacings between two grids are denoted by  $\Delta_x$  and  $\Delta_y$ , respectively. The layout may be considered as a collection of  $\Delta_x \times \Delta_y$  rectangular tiles arranged in a  $w \times h$  array.

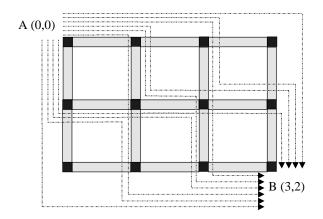

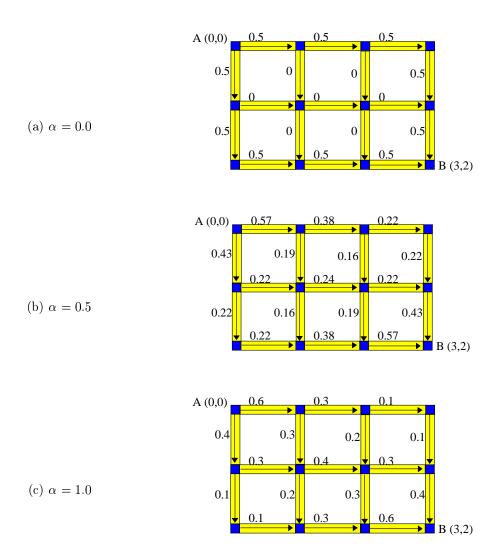

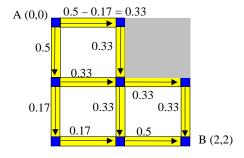

Figure 3.1: Routing between A(0,0) and B(3, 2)

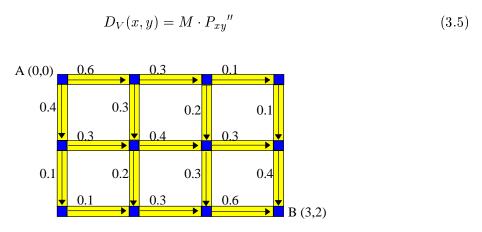

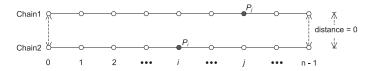

Now, consider a route from point A at (0,0) to point B at (m,n). We assume there is no routing obstacle between A and B in this section. At each grid point, the route can either go horizontally or vertically. The shortest distance between A and B is m+n, which is the Manhattan distance between the two points. If the routing is limited to the Manhattan distance, there are  $\binom{m+n}{m}$  different ways to route from A to B. The combination is derived from the fact that m tracks out of the m+n tracks are horizontal. As shown in Figure 3.1, there are  $\binom{5}{2} = 10$  different ways to route from A to B for m=3 and n=2.

Suppose all possible routes are equally probable. Let  $P_{xy}$  be the probability that the

route passes through the point (x, y). Since there are  $\binom{x+y}{x}$  different routes from (0,0) to (x,y) and  $\binom{m-x+n-y}{n-y}$  different routes from (x,y) to (m,n), we get:

$$P_{xy} = \frac{\binom{x+y}{x} \cdot \binom{m-x+n-y}{n-y}}{\binom{m+n}{m}} \tag{3.1}$$

Figure 3.2: Routing Probability through a Point

Similarly, let  $P_{xy}'$  be the routing probability that the route passes through the horizontal track from (x, y) to (x + 1, y), and  $P_{xy}''$  be the routing probability that the route passes through the vertical track from (x, y) to (x, y + 1). We get the following equations.

$$P_{xy'} = \frac{\binom{x+y}{x} \cdot \binom{m-x-1+n-y}{m-x-1}}{\binom{m+n}{m}}$$

(3.2)

$$P_{xy}'' = \frac{\binom{x+y}{x} \cdot \binom{m-x+n-y-1}{m-x}}{\binom{m+n}{m}} \tag{3.3}$$

In Figure 3.1, six out of ten possible routes pass through the horizontal track from (0,0) to (1,0). Thus,  $P_{00}{}'$  is equal to 0.6. The routing probabilities of all the horizontal and vertical tracks are shown in Figure 3.3. Suppose M wires are connected between A and B. The routing densities are defined as the product of the number of wires and the routing probabilities. Let  $D_H(x,y)$ ,  $D_V(x,y)$  be the horizontal and vertical routing densities at (x,y). We get the following equations.

$$D_H(x,y) = M \cdot P_{xy}{}' \tag{3.4}$$

Figure 3.3: Simplified Congestion Model Example

The simplified congestion model ignores many practical considerations. The following sub-sections address the issues of *via minimization*, routing between macro blocks, multi-pin nets, multiple metal layers, and routing obstacles.

#### Via Minimization

As described in Chapter 1, the interconnections usually all run in the same direction within a layer and perpendicularly between adjacent layers. This methodology supports many compact and efficient routing algorithms, and also serves the purpose of minimizing cross couplings between adjacent layers. To make a 90° turn (or bend) in an interconnect routing, a metal contact (also known as via) is needed to connect two perpendicular interconnections from one metal layer to another metal layer. Most routing algorithms minimize the number of vias because vias can cause substantial interconnect delay [Hsu83, NMN87, RKN89]. Vias between metal layers for aluminum wires are made of tungsten, and are fairly resistive. For example in a 0.25- $\mu$ m process, the resistance of a  $M_1 - M_2$  via is about 5 $\Omega$  and the resistance of a via from  $M_5$  down to the substrate can be more than 20 $\Omega$ ! Considering a 1- $\mu$ m-wide, 1-mm-long  $M_5$  line has a resistance of only 20 $\Omega$ , these resistances are very high [Ron01].

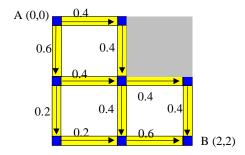

In Figure 3.1 there are ten possible ways to route from (0,0) to (3,2) with the shortest path length. Let  $W_n$  be the number of routes with n vias  $(90^{\circ} \text{ bends})$ . In this example, only two routes have a single via. Thus,  $W_1$  is 2 by definition. Similarly,  $W_2$  is 3,  $W_3$  is 4, and  $W_4$  is 3. In order to model via minimization, routes with more vias are assumed to be less probable than routes with fewer vias. We use a parameter  $\alpha$  between 0 and 1 to model this behavior. Let  $Prob\{n \ vias\}$  be the probability that the route has n vias. We define  $\alpha$

as below.

$$\frac{Prob\{n+1\ vias\}}{Prob\{n\ vias\}} = \alpha \cdot \left(\frac{W_{n+1}}{W_n}\right) \tag{3.6}$$

For simplicity,  $\alpha$  is assumed to be constant for all n. When  $\alpha$  is 1, all routes are equally probable and the model is identical to the simplified congestion model. When  $\alpha$  is 0, only routes with the minimum number of vias is allowed. In our experiments,  $\alpha$  is set to 0 for busses and very long interconnections, and  $\alpha$  is set to 0.5 for local interconnections. These configurations appear to model our designs fairly accurately.

Figure 3.4 shows the routing probabilities when  $\alpha = 0$ , 0.5, and 1. As  $\alpha$  gets smaller, the routing densities near the perimeter of the boundary box get higher. This example illustrates that the simplified model under-estimates the routing congestion near the perimeter of the boundary box, and over-estimates the routing congestion in the middle of the bounding box.

### Routing Between Macro Blocks

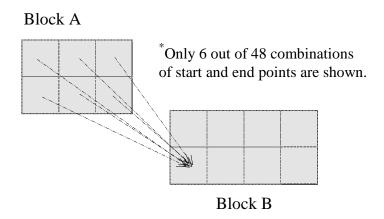

Suppose there are M wires between block  $\mathbf{A}$  and block  $\mathbf{B}$ . Traditional routing algorithms assume the wires come from the centers of the two blocks. This sometimes creates unrealistic high congestion near the centers of the blocks. There are several different ways to model routing densities. In the early design stages, the locations of the pins are unknown and the pins are modeled to be evenly distributed among all the tiles within the macro block. In the later design stages, the pins may be assigned to a certain edge and the pins are modeled to be evenly distributed among all the tiles that cover the edge. Finally, if the exact pin locations are known, the routing densities may be calculated using the congestion model between points.

In Figure 3.5, block **A** is divided into 6 tiles (2 grid lines  $\times$  3 grid lines) and block **B** is divided into 8 tiles (4 grid lines  $\times$  2 grid lines). Assuming that there are M wires connected between the two blocks. If the end points can be located anywhere within the macro blocks, there can be  $6\times8$  or 48 different combinations of start and end points. Thus, we model each of these combinations carries M/48 wires. The routing densities for all these combinations are calculated and then superimposed to give the routing densities.

Figure 3.4: Via Minimization Example

Figure 3.5: Wire Congestion Routing between Blocks Example

#### Multi-Pin Nets

The earlier part of this section focuses on how to model routing congestion caused by two-pin nets, and this sub-section describes how to model routing congestion caused by multi-pin nets. A simple way to model multi-pin nets is to decompose them to two-pin nets. There are a number of approaches to decompose a multi-pin net. One way is to assume all possible interconnections among the pins are equally possible. Thus, a N-pin net is decomposed into all possible  $\frac{N \cdot (N-1)}{2}$  two-pin nets, and each two-pin net carries  $\frac{2}{N}$  wires. The number  $\frac{2}{N}$  is derived from the fact that only (N-1) out of  $\frac{N \cdot (N-1)}{2}$  two-pin nets are required to connect the N points together, so each two-pin net only carries  $\frac{2}{N}$  wires.

If the routing algorithm is known, the congestion model can follow the same scheme to better predict the congestion. For example, if the actual router uses minimum spanning trees (MST) to decompose multi-pin nets to two-pin nets [Pri57], the congestion model should follow the same algorithm and use MST in the decomposition.

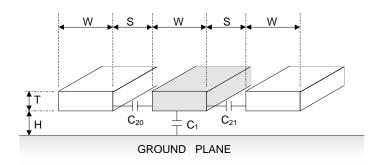

#### Multiple Metal Layers

Most modern chips utilize multiple metal layers for global and detailed routing. Typically, each metal layer has different metal width and spacing requirements. Assume every metal layer consists of either all horizontal tracks or all vertical tracks. Now, consider a metal layer with only horizontal tracks. Let  $\Delta_x$  and  $\Delta_y$  be the horizontal and vertical spacings between 2 grids, W be the metal width, and S be the metal spacing. The number of

horizontal routing channels  $(R_H)$  at each grid point is:

$$R_H = \frac{\triangle_y}{(W+S)} \tag{3.7}$$

Similarly, consider a metal layer with only vertical tracks. The number of vertical routing channels  $R_V$  at each grid point is:

$$R_V = \frac{\triangle_x}{(W+S)} \tag{3.8}$$

The horizontal and vertical channel supplies of all the metal layers are added together to obtain the horizontal and vertical channel supplies at each grid point. Routing congestion occurs when routing density exceeds channel supply, i.e.,  $D_H > R_H$  or  $D_V > R_H$ . When that happens, the routing channel is treated as a routing obstacle. On the other hand, if both horizontal and vertical tracks are permitted in every metal layer, the horizontal and vertical routing channels can be combined. In this case, routing congestion occurs when  $D_H + D_V > R_H + R_V$ .

## 3.2.2 Algorithm

This section presents a heuristic algorithm to calculate the routing probabilities based on the statistical congestion model. First, we describe how to calculate the routing probabilities between two points. The algorithm is later extended to handle routing between blocks and with routing obstacles.

#### Routing between points

The routing probabilities of all the tracks between point A and point B can be found by using the following step-by-step heuristic algorithm. The detailed derivation of the algorithm can be found in [HF97]. Following the derivation in [HF97], set  $\beta$  as in Equation 3.9.

$$\beta = \frac{2\alpha}{1+\alpha} \tag{3.9}$$

Conceptually, the constant  $\beta$  is the conditional probability that via minimization algorithm is not active in a routing. When  $\beta$  is close to 0, the routing always tries to go straight at each point because it "remembers" its previous direction. When  $\beta$  is close to 1, the

37

routing does not contain any state or memory, resembling the simplified congestion model.

Step 1: Set the probability at point  $A(P_{00})$  to 1.0.

Step 2: Calculate the probabilities at point A.

$$P_{00}' := P_{00} \cdot \frac{m}{m+n} P_{00}'' := P_{00} \cdot \frac{n}{m+n}$$

Step 3: Calculate the probabilities in the first row.

$$\begin{array}{ll} P_{10} & := P_{00}' \\ P_{10}' & := P_{10} \cdot \beta \cdot \frac{m-1}{m+n-1} + P_{00}' \cdot (1-\beta) \\ P_{10}'' & := P_{10} \cdot \beta \cdot \frac{n}{m+n-1} \\ \dots \end{array}$$

Step 4: Calculate the probabilities in the second row.

$$P_{01} := P_{00}^{"}$$

$P_{01}^{'} := P_{01} \cdot \beta \cdot \frac{m}{m+n-1}$

...

- Step 5: Repeat Step 4 for the remaining rows.

- Step 6: After all the probabilities have been calculated, do the following to ensure symmetry between A and B.

$$P_{xy} := \frac{1}{2} \left[ P_{xy} + P_{(m-x)(n-y)} \right]$$

$$P_{xy'} := \frac{1}{2} \left[ P_{xy'} + P_{(m-x-1)(n-y)'} \right]$$

$$P_{xy''} := \frac{1}{2} \left[ P_{xy''} + P_{(m-x)(n-y-1)''} \right]$$

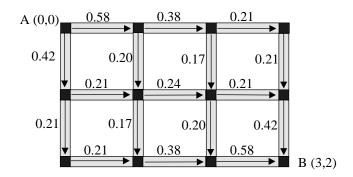

Figure 3.6 shows the routing densities from (0,0) to (3,2) with  $\alpha=0.5$  using this algorithm. The results are almost identical to the exact probabilities shown in Figure 4. When  $\alpha=0$  or 1, the results of this algorithm are exact.

Figure 3.6: Illustration of Wire Congestion Algorithm

## Routing between blocks

Suppose there are M wires between block  $\mathbf{A}$  and block  $\mathbf{B}$ ; block  $\mathbf{A}$  contains  $N_A$  tiles, and block  $\mathbf{B}$  contains  $N_B$  tiles. We can run the above algorithm  $N_A \cdot N_B$  times to calculate the routing densities, but the computation can be very slow when  $N_A \cdot N_B$  is large.

Fortunately, the original algorithm can be modified to calculate the routing densities between two blocks in a single pass. Instead of setting  $P_{00}$  to 1.0,  $P_{ij}$  is set to  $\frac{M}{N_A}$  for all (i, j) inside block **A**. This optimization is valid because routing densities can be superimposed and summed together.

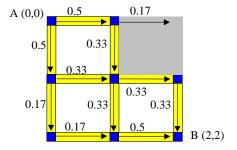

#### Routing Obstacles

Routing obstacles are common in VLSI designs. For example, some areas in a chip are reserved for local routing and cannot be used for global routing. We can model routing obstacles using the following algorithm.

- Step 1: Follow the algorithm described in the previous sub-section but ignore the routing probabilities going into the routing obstacle.

- Step 2: Re-route all the routing probabilities going into the routing obstacles back to the origin.